Soft Error Mitigation in Nanometer CMOS ICs Through Strategic Parameters considering Statistical Variations (SOMNIC)

CMOS technology scaling below the 100nm barrier convey a major paradigm related to the mechanisms that impact the reliability of integrated circuits. This paradigm shift is given by the exacerbation of the causes that may lead to circuit failures, and include physical defects (changes in circuit structure induced either during manufacturing or operation - essentially open-type defects or shorts), mechanisms caused by statistical variations (object of a past research project TEC2005-05712), or transient effects (object of our current project TEC2008-04501). Therefore, the set of possible IC defects, constituted in the past by the so-called "hard defects ", has expanded to incorporate the so-called "soft defects" or "soft errors". Hence, a modern reliability analysis of today circuits must consider the impact of a set of mechanisms that - due to scaling issues and voltage operating margins - seriously threaten the roadmap foreseen by the semiconductor industry. Various techniques have been developed to cope with "soft errors". These mitigation techniques are focused on reducing the effect of transients caused by ionizing radiation both in memory and random logic circuitry (referred to as SEU and SET events). However, these techniques do not consider the impact of statistical process variations on device and interconnect parameters thus providing a limited analysis.

In this framework, the main project objectives are:

1. Establishment of a methodology analysis based on the development of statistical compact models to determine which circuit regions are more susceptible to propagate a SET that will cause a SEU. Such a statistical models will be used to optimize SET mitigation techniques from a statistical perspective by developing a specific tool.

2. Secondly, we will focus on SRAM protection and will analyze the relationships between process parameter variations and the soft errors rate in SRAM memories. In this case, we intend to characterize the effect of variation on SRAM reliability through the application of predictive methods in various memory architectures (6T, 8T, 10T) and apply these results to mitigation improvement.

3. We have the tradition of combining rigorous theoretical studies aimed to identify and understand the underlying mechanisms and phenomenology, with the experimental verification of the methods and models developed. Therefore, in this project we planned to develop a laser-based soft errors emulation facility (whose central laser system has been already supported through FEDER funds) to verify experimentally the validity of our study and improve the state of the art

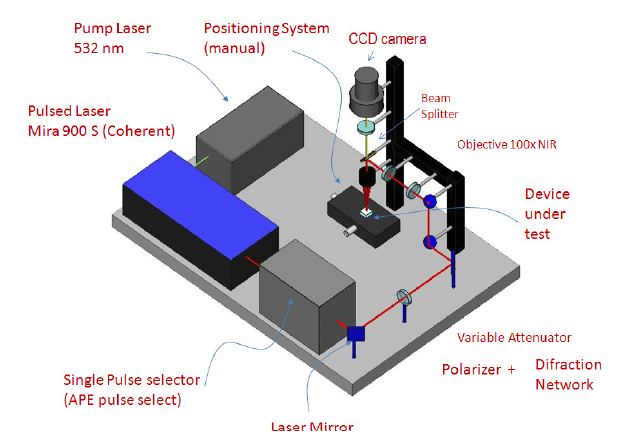

The Electronic Systems Group at UIB (GSE-UIB) group has setup a facility consisting of a Ti:Sapphire pulsed laser system.

It generates 200 fs pulses with a wavelength tunnable between 700nm and 1000nm.

The whole setup is illustrated in the following figure:

It consists of a Mira 900 (Coherent) Ti:Sapphire pulsed laser pumped by a Verdi green laser

The setup allows for a continuous or single pulse selection

A fully automated positioning system will be available soon

G. Torrens, S. Bota, B. Alorda, J. Segura

IEEE Trans. on Dev. Mat. and Rel., Vol. 14, No. 4, Dec. 2014.

We report a detailed analysis about the memory soft error rate (SER) dependence with transistor design parameters for six-transistor (6T) SRAM cells fabricated on a 65-nm CMOS commercial technology. SER data are obtained from accelerated test with an Am-241 alpha source. Five 6T cells with different nMOS and pMOS transistors size combinations were fabricated and characterized. After verifying that transistor width increase always provides higher critical charge values, SER data show that this value is improved only when increasing the pMOS transistors width. Memory cells containing non-minimum-width nMOS transistors always exhibit worse SER values than cells with minimum-size ones. In addition, one cell with a higher Qcrit than another can show a worse SER depending on the transistor type whose size is being enlarged. Accordingly to this, we have found that SER may be increased by 76% without modifying cell structure nor impacting cell area. This behavior is qualitatively and quantitatively explained through an analytical model that relates SER to Qcrit and the transistor design parameters.

B. Alorda, G. Torrens, S. Bota, J. Segura

Microelectronics Reliability, Vol. 54, No. 11, pp. 2613-2620, Nov. 2014.

We present a novel SRAM technique for simultaneously enhancing the static and dynamic noise margins in six transistor cells implemented with minimum size devices using a design for manufacturability constrained layout. During each access, the word-line voltage (VWL) is internally reduced with respect to the cell and bit-line voltages that are maintained at nominal VDD. A specific VWL can be determined for each memory region, thus allowing for an adaptive approach. The benefits and drawbacks of the technique on the overall memory performance are thoroughly investigated through both simulations and experimental data. Simulations results show that this technique expands the read margin without an appreciable increase of memory area. Specifically, an improvement of 52.6% in static noise margin and a 24.5% in critical charge (parameter used to account for the dynamic stability) has been achieved with a VWL reduction of 20%. The impact of variability on SNM is reduced, while both read and write delay increase by a specific amount that should be considered as a tradeoff when setting the word-line voltage value. A 16Kbit SRAM test chip including the proposed technique has been fabricated in a 65 nmCMOS technology. Silicon measurements confirm that the proposed technique improves cell stability during READ, which allows operating

at relatively low values of VWL with a small impact on read time.

G. Torrens, I de Paul, B. Alorda, S. Bota, J. Segura

IEEE Trans. on Nucl. Science, Vol. 61, No.4, pp.1849-1855, Aug. 2014.

Experimental results from a 65nm CMOS commercial technology SRAM test chip reveal a linear correlation between a new electrical parameter –the word-line voltage margin (VWLVM)– and the measured circuit alpha-SER. Additional experiments show that no other memory cell electrical robustness-related parameters exhibit such correlation. The technique proposed is based on correlating the VWLVM to the SER measured on a small number of circuit samples to determine the correlation parameters. Then, the remaining non-irradiated circuits SER is determined from

electrical measurements (VWLVM) without the need of additional radiation experiments. This method represents a significant improvement in time and cost, while simplifying the SER-determination methods since most of the circuits do not require irradiation. The technique involves a minor memory

design modification that does not degrade circuit performance, while circuit area increase is negligible.

S. Bota, G. Torrens, J. Verd, J. Segura

Solid-State Electronics, (Accepted for publication), 2015.

Eight-transistor (8T) cells were introduced to improve variability tolerance, cell stability and low-voltage operation in high-speed SRAM caches by decoupling the read and write design requirements. Altogether, 8T-SRAM can be designed without significant area penalty over 6T-SRAM. Ionizing radiation effects are nowadays a major concern for reliability and dependability of emerging electronic SRAM devices, even for sea-level applications. In this paper we demonstrate from experimental results that the 8T-SRAM also exhibits an enhanced overall intrinsic tolerance to radiation even though its critical charge values are smaller than conventional 6T cells. We have experimentally found that the soft error rate measured in accelerated experiments with alpha particles in SRAM devices implemented in a 65nm CMOS is 56% better for 8T cells with respect to standard 6T-cells. Even more, we show that this value can be increased up to a 200% through transistor sizing optimization in terms of cell tolerance to radiation.

X. Gili, S. Barceló, S. Bota, J. Segura

European Radiation Effects on Components and Systems Conference, RADECS 2012.

We present a noise-susceptibility analysis applied to two-inverter latch cells based on analyzing the system evolution on a state-energy map. This approach offers a description of the system dynamics providing an effective way to analyze the latch cell response to a transient event. More interestingly this method is valid to compare the latch cell robustness to SEU events of various designs.

We provide a single-value metric derived from the state-energy map related to the cell robustness against SEU events. A specific model is derived and compared to simulations from a latch cell in a 65nm CMOS commercial technology with excellent results.

J. L. Merino, S. Bota, R. Picos, J. Segura

Int. Journal of Circuit Theory and Appilcations, Vol. 41, pp. 1085-1096, 2013

The cell static noise margin (SNM) is widely used as a stability criterion for static random-access memory cells design. This parameter is typically determined through electrical simulations since direct experimentalcharacterization of SNM is not achievable. In this work, we present a methodology that provides an indirect measurement of the SNM on a per-cell basis for six transistor SRAMs. It is based on combining an Adaptive Neuro-Fuzzy Inference System (ANFIS) with circuit-level cell experimentally measurable parameters as input variables to the tool. We show that it is possible to obtain the SNM for individual memory cells using the same experimental setup and data than that required for shmoo plot measurements. Results confirm that the SNM can be experimentally estimated with a relative error compared with electrical simulations that is below 0.5%.

H. Villacorta, V. Champac, S. Bota, J. Segura

Microelectronics Reliability, Vol. 52, No. 11, pp. 2799-2804, 2012.

Resistive bridges are a major class of defects in nanometer technologies that can escape test, posing a serious reliability risk for CMOS IC circuits. The increase of process parameter variations represents a challenge for resistive bridge detection using traditional test methods, and requires more efficient test methods to be developed. In this work, we show that resistive bridge detection improves by correlating the defect-induced extra circuit delay with the power supply voltage value and the reverse body bias (RBB) applied. A Timing Critical Resistance Rtcrit is defined as a metric to quantify the resistive bridge detection enhancement in the presence of process variations under a delay based test. We show that the smaller the supply voltage, the higher the resistive bridge detection which further enhances by applying RBB. Results are presented for a 65 nm CMOS technology.